打印本文

打印本文  关闭窗口

关闭窗口 设计。

关键词: TFT-LCD ;pSiTFT ;Orcad ;集成周边驱动电路

引 言

近年来液晶产品迅速发展起来,逐渐占领了显示市场,关于液晶的各方面研究也越来越受关注。其中多晶硅TFT-LCD 逐渐应用于移动显示产品中,由于多晶硅TFT-LCD 具有薄、轻巧、高分辨率显示以及可将驱动电路集成于周边显示区域等特点,可以预计它的应用将会进一步扩展,市场份额也会逐渐增加。而周边集成驱动电路可以使大规模集成电路中的外部驱动电路和接口数量大幅度减少,成本也随之大大降低,最终实现产品的可靠性增强和整体尺寸缩小的目标。本文用Orcad 作为辅助工具,设计了行扫描和数据扫描的集成周边驱动电路,从仿真图形可以看到设计结果令人满意。

多晶硅薄膜晶体管的特性

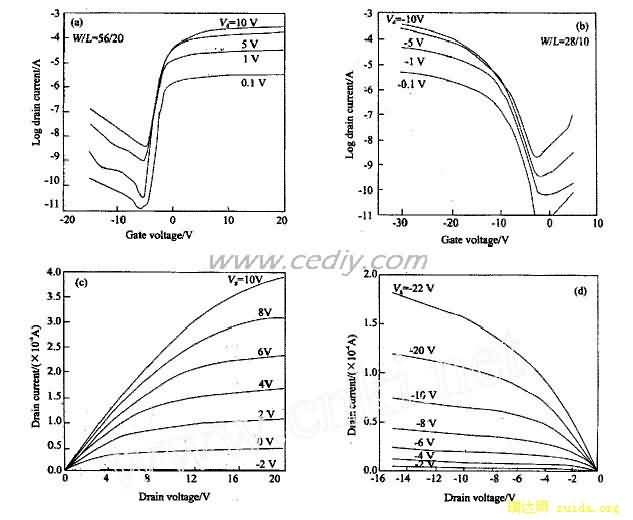

多晶硅(pSi) 是一种目前被广泛使用的半导体材料,它的迁移率很高,一般为30 cm2/V.s以上,甚至可以超过100 cm2/V.s ,由多晶硅半导体材料制备的器件能满足LCD 的驱动特性要求,从而实现驱动电路集成化设计。图1 所示为N 沟道和P 沟道pSiTFT 的特性曲线。根据特性曲线并参照有关文献,为了使设计电路中的N沟道和P 沟道pSiTFT 具有良好的开关特性,并且兼顾低功耗原则,我们采用的工作电压为:N 沟道pSiTFT 为V ds=10V,V gs=10V(开态)/Vgs=0V(关态) ;P 沟道pSiTFT为V ds=-10V,V gs=-10 V(开态)/V gs=0V(关态) 。

图1 N 沟道(a) (c) 和P 沟道(b) (d) pSiTFT 的特性曲线

周边集成驱动电路的设计

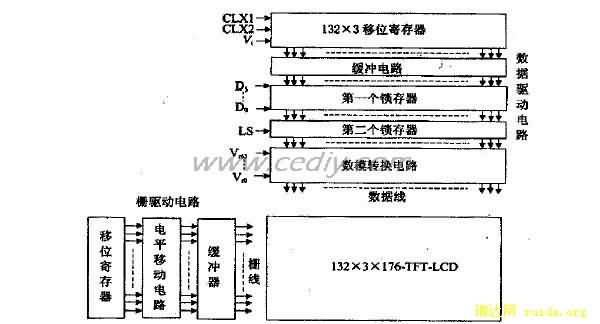

由于pSiTFT 器件的特性与用于LSI (大规模集成电路) 的MOSFET (金属氧化物半导体场效应晶体管) 的特性相同,本文利用Orcad 提供的MOS 管模型进行集成驱动电路的设计和仿真。针对132(RGB)×176 TFT-LCD 进行设计,集成周边驱动电路框图如图2 所示。其中,栅驱动电路包括移位寄存器、电平移动电路和缓冲器。数据驱动电路由移位寄存器、缓冲电路、锁存器和数模转换电路组成。栅驱动电路与栅线连接,数据驱动电路与数据线连接。

图2 周边集成驱动电路框图

栅驱动电路

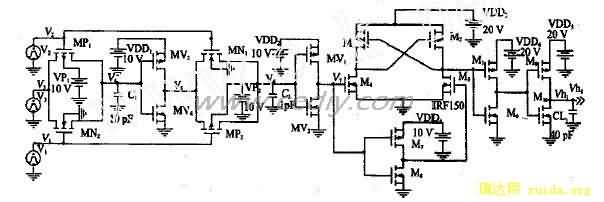

栅驱动电路的功能是产生扫描信号,使每一扫描行依次接通。扫描信号依赖于显示的构、分辨率和帧频, 扫描信号的频率f cp =f F×N , f F 是帧频, N 是扫描行数。所以当fF =60 Hz , N = 176 时,行扫描频率f cp = 60 ×176 =10 560 Hz。这样低的频率用pSiTFT形成的CMOS 移位寄存器容易实现。其次是驱动传输行的能力,也就是驱动由TFT 像素的栅电容和线电阻组成的负载能力。本设计针对的TFT_LCD 的TFT 栅电容为0.05pF 左右,再加上连线电容和寄生电容等,对于扫描驱动电路来说每一个TFT像素的电容约为0.1pF。因为所有的(132×3)TFT 的栅电容连接到一个扫描线上,所以扫描驱动电路的负载电容CL 约为40pF。因此,为了驱动这么大的电容,输出缓冲器的沟道宽度W 应取非常大,这样就有必要在移位寄存器和缓冲器之间加电平移动电路,将输出的高压与移位寄存器隔离。

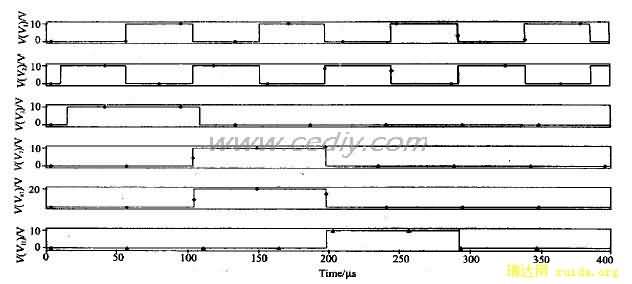

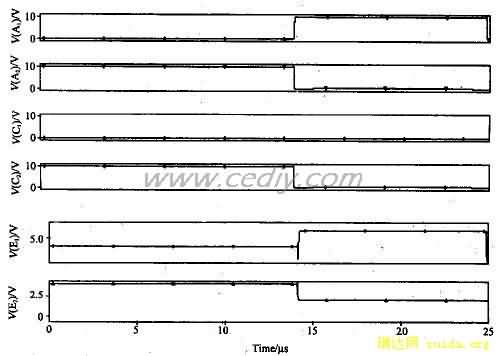

图3 为扫描驱动电路,它主要由移位寄存器、电平移动电路和缓冲器组成。移位寄存器采用双向时钟的动态移位寄存器,每一级由2 个反向器和2 个传输门组成,电荷存储在电极节点上。缓冲器由CMOS 反向器构成。移位寄存器的输入电压和缓冲器输出电压分别为10 V和20 V,负载电容CL 为40pF。图4 为时钟为10560 Hz时,移位寄存器的输出和负载为40pF 时的栅驱动电路的输出波形的仿真结果。其中, V1 、V2 为互补的双向时钟; V3 为移位寄存器的移位数据输入波形; V7 、V11 为移位寄存器的第一级、第二级输出波形,电压幅值为10V; Vn1为V7 经过电平移动电路和两级缓冲器后的输出波形,作为栅驱动电路的输出,电压幅值为20V(通过电平移动电路实现了高压隔离输出) 。如果显示器像素比较多,可以增加反相器的个数或增大反相器的尺寸W/L ( L 为沟道长度) 来增加带载负载能力。

图3 栅驱动电路

数据驱动电路

数据驱动电路相对来说是比较复杂的,它必须完成串行2并行的转换和数字信号到模拟信号的转换,以提供适当的模拟电压供给数据线。电压值在时间平均上必须接近零,以防止液晶老化变坏,因此加到每个像素上的电压极性要与前一帧极性相反。数据驱动电压要足够大,以适合驱动正负极性的信号,正常需要幅度在10 V左右。数据驱动所设定的输出时间必须足够快,也就是说在扫描行周期内,有足够的时间把数据传输给像素,pSi TFT 像素信号传输只占几个微秒。数据输入频率为f DT=fF ×N×M , 其中f F 为帧频, N 和M 分别为行和列数。对于(132×3)×176点的显示屏,如果帧频为60Hz ,则f DT=60×132×3×176≈4.18 MHz。

图4 时钟、移位寄存器输出和栅驱动器输出( CL = 40pF)

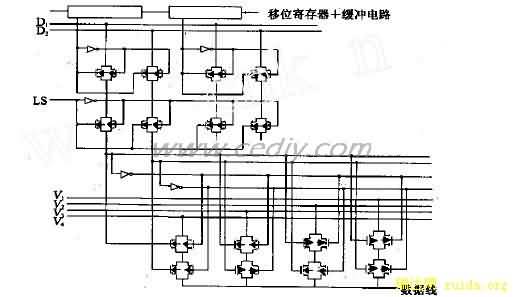

如图2 中的数据驱动电路部分,它主要由移位寄存器、缓冲电路、锁存器和数模转换电路(DAC) 组成。移位寄存器仍采用栅驱动电路使用的双向时钟的动态移位寄存器,CLK1/2 为双向移位时钟, Vi 为移位寄存器的移位起始脉冲。缓冲电路由CMOS 反相器构成。锁存器由传输门和CMOS 反相器构成,D5~D0 为6 位灰度级显示数据(D5 为最高有效位,D0 为最低有效位) ,LS 为锁存开关信号。在移位寄存器输出脉冲的控制下, (132 ×3) 个6 位的数字信号依次锁存到第一个锁存器中,结果串行的数字信号变换成并行的数字信号,然后在LS 的控制下并行输出到数模转换电路中。数模转换电路也是由传输门和CMOS 反相器组成, Vr63~ Vr0为驱动液晶像素显示的模拟电压。6位的数字信号则需要6 ×26个传输门,其中每6 个传输门通过各自高、低两个输入端对6 位数字信号选取的不同组合可以将一个6位的数字信号转换为模拟信号VrN 中的一个, 从而通过26 种组合输出26 个灰度级,最终实现数模转换。实际上,这种数模转换电路相当于六选一的数据选择器,图5 显示了2 位4 个灰度级时的数据驱动电路图。

图5 数据驱动电路

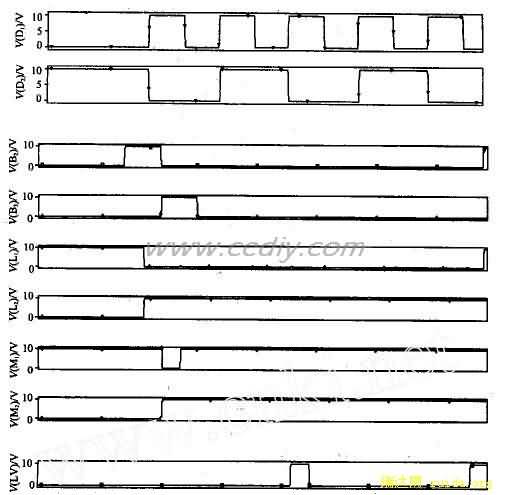

由于电路复杂,这里仅显示两位4 个灰度级(参考模拟电压分别为8 V,6 V,4 V,2 V,对应灰度级数据为11 ,10 ,01 ,00) 时的数据驱动电路仿真波形,为了便于观察比较波形,时序上也作了适当调整,如图6 所示。

图6 中,D1 、D2 为输入的2 位数字信号,D1为高位,D2 为低位。图中给出的第一组灰度级数据为10 ,第二组为00 。B2 、B3 为移位寄存器的输出,用于控制灰度级数据的传输。L1 、L2 为保存于第一个锁存器中的第一组灰度级数据,由于使用了一级反相缓冲器,其输出为01 ;M1 、M2 同理,输出为11 。LV为锁存开关信号,它为高电平时,将保存于第一个锁存器中的所有灰度级数(实际为6 位时,共132×3×6 位数据) 并行输出至第二个锁存器并经过DAC 送至数据线。A1 、A2 为保存于第二个锁存器中的第一组灰度级数据,由于使用了一级反相缓冲器,其输出为10 ,C1 、C2 同理,输出为00。第二个锁存器中的数据经过DAC,转换为模拟电压值,E1 为6V,E2 为2V,即输出的模拟电压与输入的灰度级数据的对应关系与计设目的一致。根据需要,还可以在数模转换电路的输出端加上输出电路后再将其输出至数据线。

图6 数据驱动电路的时序波形

结 论

因为小尺寸液晶屏像素少,所以驱动电路的负载电容相对较小,驱动电路结构相对简单。由此可见,小尺寸液晶屏的驱动电路易于进行周边集成化的设计。本文利用Orcad 提供的MOS 管模型,针对132RGB×176TFT-LCD 的相关参数进行集成驱动电路的设计和仿真。从仿真的结果看出,设计可以满足对小尺寸液晶屏的驱动要求。通过对器件参数的进一步优化调整和电路功能的进一步完善,就可以把设计的栅驱动器和数据驱动器集成到玻璃上,从而实现驱动电路的周边集成化。

打印本文

打印本文  关闭窗口

关闭窗口