打印本文

打印本文  关闭窗口

关闭窗口 关键词:脉冲压缩;线性调频;ADSP-TS101S;匹配滤波器

1 引 言

脉冲压缩解决了雷达作用距离与分辨率之间的矛盾,是雷达系统中较为成熟和经常采用的技术。

随着数字技术和大规模集成电路技术的飞速发展,数字脉冲压缩技术以其性能稳定,抗干扰能力强,控制方式灵活和硬件系统小型化程度高等优点,成为现代雷达脉冲压缩系统的发展趋势。特别是高性能、高速DSP的不断推出,为进一步增强系统的性能和集成度提供了可能。目前,在脉冲压缩系统中应用最多的两种雷达信号是线性调频信号和相位编码信号。线性调频信号的突出优点是匹配滤波器对回波信号的多普勒频移不敏感,而且这种波形易于得到比较大的压缩比。本文研究线性调频信号采用ADSP-TS101S实现雷达脉冲压缩的工程实现技术。

2 ADSP-TS101S介绍

ADSP-TS101S是一款高性能的静态超标量处理器,针对大的信号处理任务和通信结构进行了优化。该处理器将非常宽的存储器宽度和双运算模块(支持32-b浮点和8-,16-,32-,和64-b定点处理)组合在一起,建立了数字信号处理器性能的新标准。TigerSHARC静态超标量结构使DSP每周期能够执行多达4条指令,24个16-b定点运算和6个浮点运算。

ADSP-TS101S的运行速度为250MHz,4ns指令周期;6 Mb片内SRAM;双运算模块:每个包含一个ALU,一个乘法器,一个移位器和一个寄存器组;双整数ALU,提供数据寻址和指针操作功能;一个外部端口,4个链路口,SDRAM控制器,可编程标志引脚,2个定时器和定时器计满引脚等用于系统集成;用于片上仿真的IEEE1149.1兼容的JTAG接口;用于通过共享总线无缝连接多达8个TigerSHARCDSP的片内总线仲裁。

ADSP-TS101S的主要优点是提供高性能静态超标量DSP操作,专门优化适用于通信和其他的需要多DSP处理器的应用;杰出的DSP算法和I/O性能表现(I/O性能如表1所示);DMA控制器支持14个DMA通道,可完成片内存储器、片外存储器、存储器映射外设、链路口、主机处理器和其他(多处理器)DSP间的低开销传输;非常灵活的指令集和支持友好的高级语言的DSP结构使DSP编程方便。

ADI公司提供一套完整的ADSP-TS101S软硬件开发工具,包括仿真器和VisualDSP++TM开发环境。仿真器能够对ADSP-TS101S实现全仿真,还支持对其他ADI的tigerSHARC DSP芯片的仿真。ADI公司的DSP仿真器使用ADSP-TS101S的IEEE1149.1JTAG测试访问端口,在仿真时监视和控制目标板上的DSP处理器。仿真器提供全速仿真,允许查看和修改存储器、寄存器和处理器堆栈。使用处理器JTAG接口可确保进行不干扰处理器运行的在电路仿真——仿真器不影响目标系统的装载和定时。

3 脉压的实现与仿真

3.1 算法框图

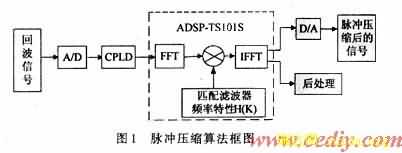

用ADSP-TS101S实现脉压的算法框图如图1所示。

根据算法框图,回波信号为线性调频信号,经高速A/D采样后,数据在CPLD内与系数cosφ,sinφ相乘,经低通滤波后输出I,Q两路正交数据。A/D采样时钟由CPLD给出。ADSP-TS101S作脉压处理,实现FFT,匹配相乘,IFFT。然后将数据交后续处理,同时通过D/A变换,可得脉冲压缩后的视频模拟信号。

3.2 数据段的脉压处理

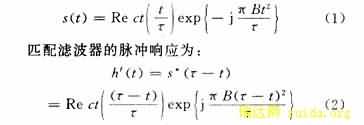

数据段的雷达视频信号可表示为:

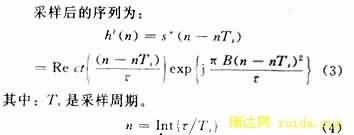

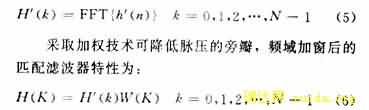

按照式(3)产生数据,其中n按照-n/2~n/2的顺序取值。作N点FFT有:

其中:W(k)是窗函数的FFT。

按照式(6)产生匹配滤波器的频率特性H(k),存放在存储器中,按照图1给出的算法进行脉冲压缩处理。

3.3 软件流程图

图2为脉冲压缩软件流程图。

初始化主要是完成所需DMA以及外部中断的初始化。握手信号为CPLD发送过来的DMA启动信号,接ADSP-TS101S的某个外部中断管脚,一旦中断产生,立即启动DMA,利用DMA接收一组新的线性调频数据脉压数据,放入内存中。

DMA采用外部请求发送方式,所以CPLD应该发送给ADSP-TS101S的对应DMA的DMARx管脚一个数据发送同步信号。双口内存是用ADSP-TS101S的片内存储器虚拟的,其具体方法为:

开辟2个存储内存,设为高端内存和低端内存,同高,就使用高端内存,否则就使用低端内存,存储结束,对memlh变量取反。在读取时,当memlh为高时,核就读取低端内存,否则就读取高端内存。在读取操作中,不对memlh操作。脉压处理由ADSP-TS101S的核来完成,完成定点到浮点的转换,FFT运算,与存储器内的脉压参数相乘,IFFT运算,数据截取。发送数据分成2路,一路利用外部DMA发送至D/A,另一路发送给后续处理,用链路口或者外部总线方式都可以。

3.4 实验结果

由雷达前端接收机接收一个以800μs为周期,宽度为120μs,载频为30 M的线性调频信号,信号带宽为2 M。用8 M时钟进行A/D采样,采样到的数据输入到CPLD进行正交解调,然后以4 M的速率以DMA方式传送给ADSP-TS101S,进行脉压处理。取前310μs,即1240点作2048点FFT,不够的数据补零。然后与存放在存储器中的匹配滤波器的频率特性H(k)相乘,作2048点IFFT,时域加海明窗。ADSP-TS101S采用4倍频时钟,即160 M时钟,一次FFT时间为150μs左右。整个脉压过程约为350μs左右。

图3为2 M带宽,120μs长度的线性调频信号经过ADSP-TS101S脉压前后的波形图。

(1)ADSP-TS101S有3级复位:上电复位、正常复位和内核复位。

上电复位 系统上电且Strap选项稳定后,

正常复位 上电复位后的任何复位,

内核复位 设置SQCTL寄存器的SQRST位后内核被复位,但不影响外部端口和I/O。建议使用CPLD作复位电路,以确保ADSP-TS101S复位正常,系统正常工作。

(2)电源和地之间应合理分布去耦电容。在ADSP-TS101S芯片背面的水平和垂直的4个不同方向放置4个电容,大小为0.1μF,整个印制板还要配置若干大容量坦电容(47μF)进行去耦。

(3)TigerSharc并不直接支持内部-内部存储器间的数据传送,需要通过多处理器空间完成,TigerSharc的链路口与以前Sharc的链路口不兼容。

(4)必须打开全局中断向量,才能响应中断。在DMA方式传输数据时,最好先使能链路口。

(5)所有没有用于引导的链路口的DMA通道必须进行清除、重新初始化操作。如果DMA通道没有停用,则链路中断机制不起作用。同时,链路口也需重新初始化。

4 结 语

由于ADSP-TS101S为大的信号处理任务进行了优化,有非常宽的存储器宽度,支持浮点和定点处理,使实时脉冲压缩具有高速度、高性能的特性,并有电路板面积小、性价比高、功耗低、应用开发时间周期短的特点,使其具有重要的现实应用。

参考文献

[2] 丁玉美,高西全.数字信号处理[M].西安:西安电子科技大学出版社,2001.

[3] TigerSHARCDSPhardware specification part#ADSP TS101S.Analog Devices,Inc.2002.

[4] TigerSHARCDSPinstruction set specification Part#ADSP-TS101S.Analog Devices,Inc.2002.

[5] TigerSHARC DSP ADSP-TS101S datasheet,Analog Devices,Inc.2002.

打印本文

打印本文  关闭窗口

关闭窗口