打印本文

打印本文  关闭窗口

关闭窗口 【性能 参数】

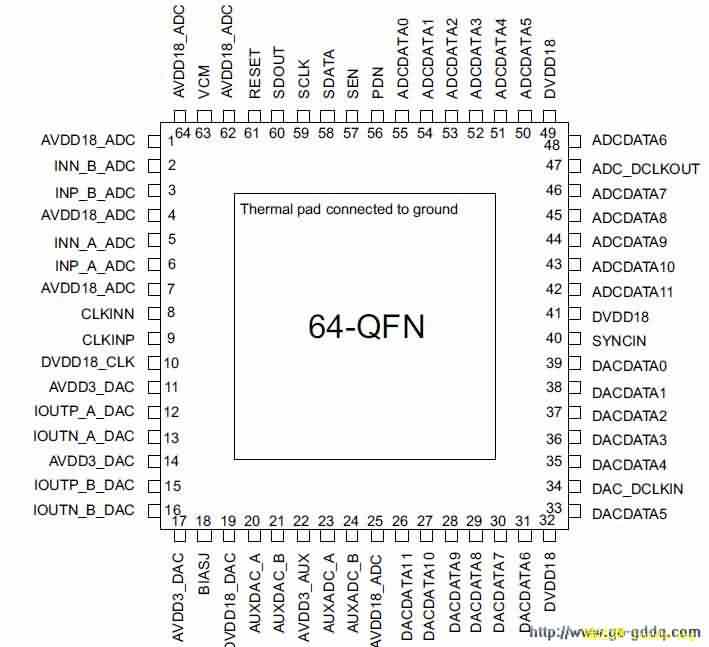

采用64脚QFN封装,该器件集成双通道65 MSPS ADC与双通道130 MSPS DAC,全双工运行时功耗仅为398mW,全速半双工接收模式下,功耗则为212mW。

主要特性:

低功耗:深度睡眠模式(deep-sleepmode)下功耗仅为12mW,唤醒时间仅13us,在轻度睡眠模式(light-sleepmode)下功耗仅为120mW,唤醒时间则为5us;

高性能支持更清晰信号:针对3GW-CDMA蜂窝信号,双通道ADC可实现70dB的SNR,而双通道DAC则可实现75dB的相邻通道泄漏比(adjaceNTChannelleakageratio);

信号处理可降低FPGA闸门数量、接口速度与成本:二者都支持独立收发数字模块上下转换,提供2x至4x内插(interpolation)、2x抽取(decimation)、粗调(coarse)及32位NCO频率混合器、针对正交调制收发的增益、相位及偏置数字校正,以及峰值/rms功率计;

高集成度降低系统成本:双通道12位辅助DAC及双通道输入12位辅助ADC,可减少独立监控与控制器件,节省板级空间,降低功耗与成本;

为设计人员实现高灵活性:数字DAC输入与ADC输出可针对串行LVDS进行配置,减少引脚/轨迹数(trace-count),协助实现长轨迹信号传输(long-tracesignaling)。低功耗接口的多路复用12位CMOS也支持两条总线上的全双工,或一条至两条数字总线的半双工;

引脚排列图:

打印本文

打印本文  关闭窗口

关闭窗口