摘要:使用TI公司C5000系列DSP中的TMS320C542构成了一个数据采集处理系统,介绍了系统的结构、性能、工作流程及设计的注意事项。

关键词:TMS320C542 数据采集处理 CPLD

近年来,随着DSP技术的普及,一大批低价格、高性能DSP芯片的出现,越来越多的电子工程技术人员开始使用DSP来进行系统设计。本文以TI公司C5000系列DSP中的TMS320C542为例,构成一种数据采集处理系统。文中详细地分析了系统的结构、设计的注意事项、HPI接口的工作原理与连接方法、系统的工作流程以及软件编制中的注意事项。

1 TMS320C542结构及应用

TMS320C542是TI公司C5000系列DSP中的一种,C5000系列共有的特点如下:

·改进的哈佛结构,包含一条程序总线,三条数据总线和四条地址总线

·高度并行的CPU和针对应用优化的硬件

·针对算法和高级语言优化的指令集

·先进的IC技术使其既高性能又低功耗

C5000系列内部硬件功能块如图1所示。其中,有:40bit算数逻辑单元(ALU);两个40bit累加器A和B;17×17bit乘加单元(40bitMAC ,可作64级FIR运算而不必考虑溢出; 计算、选择、存储单元(CCSU),特别适合Viterbi等算法;40bit桶型移位寄存器;片上双存取RAM,每机器周期可存取两次;片上单存取RAM,可同时访问两块片上存储区;片上外围接口,包括串口、定时器、PLL、HPI接口等。

计算、选择、存储单元(CCSU),特别适合Viterbi等算法;40bit桶型移位寄存器;片上双存取RAM,每机器周期可存取两次;片上单存取RAM,可同时访问两块片上存储区;片上外围接口,包括串口、定时器、PLL、HPI接口等。

TMS320C542自身特点如下:

·25ns单周期定点指令执行时间,5V供电

·10K Words16bit 片上双存取RAM

·64K Words程序,64K Words数据,64K Words I/O存储空间

·2K Words HPI接口,可通过此接口方便地与主设备进行信息交换,主设备也可通过此接口下载DSP程序

·一个自动缓冲的串口和一个TDM串口,且都可用作标准同步串口

此外,C5000系列DSP可使用JTAG接口进行调试,可完全控制DSP上的所有资源,使用方便可靠。

1 TMS320C542结构及应用

TMS320C542是TI公司C5000系列DSP中的一种,C5000系列共有的特点如下:

·改进的哈佛结构,包含一条程序总线,三条数据总线和四条地址总线

·高度并行的CPU和针对应用优化的硬件

·针对算法和高级语言优化的指令集

·先进的IC技术使其既高性能又低功耗

C5000系列内部硬件功能块如图1所示。其中,有:40bit算数逻辑单元(ALU);两个40bit累加器A和B;17×17bit乘加单元(40bitMAC ,可作64级FIR运算而不必考虑溢出;

计算、选择、存储单元(CCSU),特别适合Viterbi等算法;40bit桶型移位寄存器;片上双存取RAM,每机器周期可存取两次;片上单存取RAM,可同时访问两块片上存储区;片上外围接口,包括串口、定时器、PLL、HPI接口等。

计算、选择、存储单元(CCSU),特别适合Viterbi等算法;40bit桶型移位寄存器;片上双存取RAM,每机器周期可存取两次;片上单存取RAM,可同时访问两块片上存储区;片上外围接口,包括串口、定时器、PLL、HPI接口等。TMS320C542自身特点如下:

·25ns单周期定点指令执行时间,5V供电

·10K Words16bit 片上双存取RAM

·64K Words程序,64K Words数据,64K Words I/O存储空间

·2K Words HPI接口,可通过此接口方便地与主设备进行信息交换,主设备也可通过此接口下载DSP程序

·一个自动缓冲的串口和一个TDM串口,且都可用作标准同步串口

此外,C5000系列DSP可使用JTAG接口进行调试,可完全控制DSP上的所有资源,使用方便可靠。

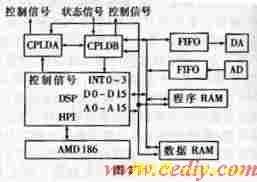

2 系统结构

由TMS320C542构成的数据采集处理系统的结构如图2所示,以DSP为中心,带有64K程序RAM,64K数据RAM,并通过16K×16的FIFO将数据送到DA,16K×16的FIFO将AD采集的数据送到DSP。与主机通过HPI接口进行数据交换。对SRAM、FIFO、AD、DA的控制,DSP所需各种状态信息的获取,以及与主机的其它一些联系,都通过CPLDA和CPLDB来实现。

由TMS320C542构成的数据采集处理系统的结构如图2所示,以DSP为中心,带有64K程序RAM,64K数据RAM,并通过16K×16的FIFO将数据送到DA,16K×16的FIFO将AD采集的数据送到DSP。与主机通过HPI接口进行数据交换。对SRAM、FIFO、AD、DA的控制,DSP所需各种状态信息的获取,以及与主机的其它一些联系,都通过CPLDA和CPLDB来实现。

C5000系列DSP关键的外部接口信号如下:

·A0~A15,地址总线

·D0~D15,数据总线

·/MSTRB,外部存储器存取闸

·/IOSTRB,I/O存取闸

·R/W,读写信号

·/PS,程序空间选择

·/DS,数据空间选择

·/IS,I/O空间选择

·READY,数据准备好

此外,还有/HOLD、/HOLDA等,本系统未用。

2.1 存储器控制

程序存储器和数据存储器各使用一片64K×16的SRAM,为了使DSP对外存的操作尽量快,其速度等级为12ns。使用/PS作程序存储器的片选,

/DS作数据存储器的片选,而两片存储器的读写信号如下:

/DS作数据存储器的片选,而两片存储器的读写信号如下:/OE=not(not(/MSTRB) and not(R/W))

/WR=notnot(/MSTRB) and (R/W)

出于高速的需要,采用了Xilinx公司的XC9536生成逻辑(CPLDA)。XC9536管脚至管脚的延迟为5ns,内部有36个宏单元,可用管脚34个,可在线编程,使用起来有很多优点。通过这些措施,系统可零等待地存取程序和数据RAM,也就是说,存储器读可达40M×16bit,写可达20M×16bit。

2.2 FIFO控制

用于DAFIFO的写和ADFIFO的读都由CPLDA产生,其逻辑方程为:

/ADFIFOR=not(not(/IOSTRB) and not(R/W) and ADDR0x0)

/DAFIFOW=not(not/IOSTRB) and R/W and ADDR0x0)

其中,ADDR0X0指DSP的A15~A13为零。

DIFIFO由两片容量16K×9bit、速度10ns的FIFO构成,ADFIFO亦如此。由于控制信号的低延迟和FIFO的高速,对FIFO的存取也达到了零等待,即:使用RPT或RPTZ指令时,可达20M×16bit/s。

2.3 A/D和D/A控制

A/D转换器负责将外部模拟信号变换成DSP可处理的数字量,是DSP进行处理的基础,在系统中具有十分重要的地位,采用的是10M采样率、12bit分辨率的AD9220,如果需要,可在不改板的情况下换成20M或40M采样率的A/D。而D/A则将DSP生成的数字信号变成模拟量,完成信号的输出或对系统其他部分的控制,采用了100M速度的AD9762。A/D和D/A的控制信号如下:

·ADCLK和DACLK,分别是A/D转换器和D/A转换器的时钟

·ADFIFOW,将A/D转换的数据写入ADFIFO

·DAFIFOR,从DAFIFO读出数据以供D/A转换

·DAFIFOMR和DAFIFORT,用于DAFIFO的清零和重传

·ADFIFOMR和ADFIFORT,用于ADFIFO的清零和重传

此六个信号都由CPLDB产生,CPLDB采用的是Xilinx公司的XC95108,速度为10ns,有108个宏单元,可在线编程,因而有较高的灵活性。使用24MHz的晶振为CPLDB提供时钟,由DSP通过I/O口向CPLDB写入数据以控制ADCLK和DACLK的开关和频率,并以I/O写的方式产生FIFO的清零和重传信号。

2.4 CPLDA和CPLDB的应用

由以上介绍可以看出, 整个系统的逻辑都由CPLDA和CPLDB产生。此外,它还有以下功能:

整个系统的逻辑都由CPLDA和CPLDB产生。此外,它还有以下功能:

用于DAFIFO的写和ADFIFO的读都由CPLDA产生,其逻辑方程为:

/ADFIFOR=not(not(/IOSTRB) and not(R/W) and ADDR0x0)

/DAFIFOW=not(not/IOSTRB) and R/W and ADDR0x0)

其中,ADDR0X0指DSP的A15~A13为零。

DIFIFO由两片容量16K×9bit、速度10ns的FIFO构成,ADFIFO亦如此。由于控制信号的低延迟和FIFO的高速,对FIFO的存取也达到了零等待,即:使用RPT或RPTZ指令时,可达20M×16bit/s。

2.3 A/D和D/A控制

A/D转换器负责将外部模拟信号变换成DSP可处理的数字量,是DSP进行处理的基础,在系统中具有十分重要的地位,采用的是10M采样率、12bit分辨率的AD9220,如果需要,可在不改板的情况下换成20M或40M采样率的A/D。而D/A则将DSP生成的数字信号变成模拟量,完成信号的输出或对系统其他部分的控制,采用了100M速度的AD9762。A/D和D/A的控制信号如下:

·ADCLK和DACLK,分别是A/D转换器和D/A转换器的时钟

·ADFIFOW,将A/D转换的数据写入ADFIFO

·DAFIFOR,从DAFIFO读出数据以供D/A转换

·DAFIFOMR和DAFIFORT,用于DAFIFO的清零和重传

·ADFIFOMR和ADFIFORT,用于ADFIFO的清零和重传

此六个信号都由CPLDB产生,CPLDB采用的是Xilinx公司的XC95108,速度为10ns,有108个宏单元,可在线编程,因而有较高的灵活性。使用24MHz的晶振为CPLDB提供时钟,由DSP通过I/O口向CPLDB写入数据以控制ADCLK和DACLK的开关和频率,并以I/O写的方式产生FIFO的清零和重传信号。

2.4 CPLDA和CPLDB的应用

由以上介绍可以看出,

整个系统的逻辑都由CPLDA和CPLDB产生。此外,它还有以下功能:

整个系统的逻辑都由CPLDA和CPLDB产生。此外,它还有以下功能:·FIFO的所有状态信号,系统外部送入的各种控制和状态信号,都送入了CPLDB,可由DSP通过I/O方式读取

·DSP的四个外部中断、NMI中断都连至CPLDB,可通过I/O口实时控制哪个信号接入哪个中断,具有较大的灵活性

·DSP的通用I/O管脚BIO和XF连至CPLDA,可以查询方式快速响应外部信号

·主机对DSP的复位和其它一些特征的控制,对DSP的某些信息的读取

·DSP对其它一些外围电路的控制

由于在硬件设计时,对实际应用的要求并不能完全了解,因此需要使系统有足够的冗余和灵活性,使用CPLD可以达到这一要求。通过将可能需要的各种控制和状态信号引入CPLD,并利用CPLD的大容量和现场可编程性,可根据不同的要求进行现场修改,从而使系统设计的成功率更大,并且有很大的灵活性。

系统中使用了两片CPLD,而没有用一片大容量的CPLD代替,是出于系统性能的考虑。因为存储器和FIFO的读写信号需要较低的延迟才可满足零等待的要求,而大容量的CPLD延迟大且价格高,因而用XC9536满足系统对速度的要求,而用XC95108满足系统复杂逻辑对容量的要求。

·DSP的四个外部中断、NMI中断都连至CPLDB,可通过I/O口实时控制哪个信号接入哪个中断,具有较大的灵活性

·DSP的通用I/O管脚BIO和XF连至CPLDA,可以查询方式快速响应外部信号

·主机对DSP的复位和其它一些特征的控制,对DSP的某些信息的读取

·DSP对其它一些外围电路的控制

由于在硬件设计时,对实际应用的要求并不能完全了解,因此需要使系统有足够的冗余和灵活性,使用CPLD可以达到这一要求。通过将可能需要的各种控制和状态信号引入CPLD,并利用CPLD的大容量和现场可编程性,可根据不同的要求进行现场修改,从而使系统设计的成功率更大,并且有很大的灵活性。

系统中使用了两片CPLD,而没有用一片大容量的CPLD代替,是出于系统性能的考虑。因为存储器和FIFO的读写信号需要较低的延迟才可满足零等待的要求,而大容量的CPLD延迟大且价格高,因而用XC9536满足系统对速度的要求,而用XC95108满足系统复杂逻辑对容量的要求。

2.5 HPI接口

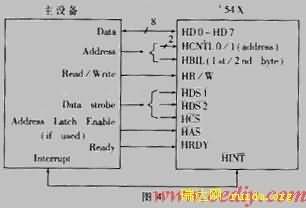

DSP可使用HPI(Host Port Interface 接口方便地与主设备或主处理器交换数据,而几乎不需增加额外的器件。对40MHz主频的320C542而言,通信速度最快可达64Mbps。而且C5000系列DSP通过某种连线方式,可利用HPI接口下载程序,从而使系统具有更大的灵活性。HPI接口的框图如图3所示,有HPIA(HPI地址寄存器)、HPID(数据寄存器)、HPIC(控制寄存器)三个16bit寄存器,主设备就是通过这些专用寄存器与HPI通信。在C542的10K内部RAM中,有2K字属于HPI存储块。系统框图如图4所示,HD0~HD7是8位数据线,直接连到主设备的数据线上;HCS为片选信号;HDS1和HDS2为数据锁存信号,在主设备的存取周期控制数据的传输,一般连至主设备的数据选通;HR/W决定当前操作是读还是写,可根据主设备的具体情况决定与何种信号相连;HCNTL0/1用于主设备选择存取HPI的哪一个寄存器和对寄存器的存取类型,连至主设备的地址线;由于HPI寄存器是16位,而HPI与主设备仅以8位数据线相连,因而用HBIL决定当前存取的是一个字的第一还是第二字节,连至主设备的地址线。

对HPI进行操作,首先要将控制字写入HPIC,然后将要存取的地址写入HPIA,最后存取HPID,就可从HPI存储块读数或将数据写入HPI存储块。此外,还可选择HPIA自动增加方式,将初始地址写入HPIA后,可不再操作HPIA,每存取一次数据,地址都会自动加一,因而大大加快了存取速度。

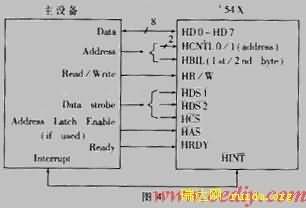

在本系统中,主设备是AMD186构成的嵌入式系统,AMD与HPI的连接如图5所示。由以上介绍可以看出,使用HPI也可与PC机的ISA总线方便地连接, 用PC机作为主设备,通过PC机向DSP下载程序完成各种功能。

用PC机作为主设备,通过PC机向DSP下载程序完成各种功能。

DSP可使用HPI(Host Port Interface 接口方便地与主设备或主处理器交换数据,而几乎不需增加额外的器件。对40MHz主频的320C542而言,通信速度最快可达64Mbps。而且C5000系列DSP通过某种连线方式,可利用HPI接口下载程序,从而使系统具有更大的灵活性。HPI接口的框图如图3所示,有HPIA(HPI地址寄存器)、HPID(数据寄存器)、HPIC(控制寄存器)三个16bit寄存器,主设备就是通过这些专用寄存器与HPI通信。在C542的10K内部RAM中,有2K字属于HPI存储块。系统框图如图4所示,HD0~HD7是8位数据线,直接连到主设备的数据线上;HCS为片选信号;HDS1和HDS2为数据锁存信号,在主设备的存取周期控制数据的传输,一般连至主设备的数据选通;HR/W决定当前操作是读还是写,可根据主设备的具体情况决定与何种信号相连;HCNTL0/1用于主设备选择存取HPI的哪一个寄存器和对寄存器的存取类型,连至主设备的地址线;由于HPI寄存器是16位,而HPI与主设备仅以8位数据线相连,因而用HBIL决定当前存取的是一个字的第一还是第二字节,连至主设备的地址线。

对HPI进行操作,首先要将控制字写入HPIC,然后将要存取的地址写入HPIA,最后存取HPID,就可从HPI存储块读数或将数据写入HPI存储块。此外,还可选择HPIA自动增加方式,将初始地址写入HPIA后,可不再操作HPIA,每存取一次数据,地址都会自动加一,因而大大加快了存取速度。

在本系统中,主设备是AMD186构成的嵌入式系统,AMD与HPI的连接如图5所示。由以上介绍可以看出,使用HPI也可与PC机的ISA总线方便地连接,

用PC机作为主设备,通过PC机向DSP下载程序完成各种功能。

用PC机作为主设备,通过PC机向DSP下载程序完成各种功能。要使用HPI下载程序,只需在DSP复位时将程序通过HPI接口写入HPI存储块从0X1000开始的存储区,并在上电复位后的一段时间将HINT管脚的信号引至INT2管脚,DSP在Boot程序中检测到后,就会自动跳转至0X1000处开始执行。

3 系统工作流程及设计注意事项

系统通过实际测试,运行速度为40MIPS,程序和数据存储器、所有I/O口都能全速运行,工作稳定可靠。其工作流程如下:

(1)根据要求编写DSP程序并调试通过。

(2)复位DSP,并由主设备通过HPI接口向DSP下载程序。

(3)复位信号失效,DSP在主设备的控制下开始工作。

由于系统工作于较高的频率下(CPU为40MHz,外围设备一般为20MHz,最高为40MHz),因而在系统设计中,必须注意高频影响。

首先,系统要尽量简单,要选择大容量、表面封装的元器件,以使元件数量少、体积小,降低信号反射并有利于布线。

其次,在设计PCB板时,要采用四层板,中间两层作电源和地,并多加一些去耦电容。布线时不可用90度的拐弯,过孔要尽量少。数据和地址最好成组布线,以降低对其它信号的影响。一些关键的控制线,如存储器读写信号和FIFO读写信号,最好在其两边加地线保护。特别是FIFO的读写信号,由于其对干扰特别敏感,要特别注意。对一些较长的引线,可串接一个30Ω的小电阻或加终端匹配以减小反射。

4 C5000系列DSP的软件编程和调试

C5000系列DSP的编程工具,有C语言和汇编语言两种,而汇编语言又有两种指令集,一种叫记忆指令集(Mnemonic Instruction Set ,类似8086的汇编语言;一种叫代数指令集(Algebraic Instruction Set ,类似于C语言,使用起来比记忆指令集方便很多。

实际应用中,一般都是C和汇编混合编程,混合编程的方法,可查阅C5000系列DSP的手册得到。TI公司还提供了一个运行库(Runtime Lib ,用TI公司的JTAG调试器进行调试时,在DSP程序中调用运行库的函数,可以打开PC机上的文件获取数据,或将DSP的数据传入PC机并存入文件,或通过PC机键盘向DSP传递信息和发送命令,总之,可以为调试带来极大的方便。

在本系统中,由于既有A/D,又有D/A,构成了一个闭环,自发自收。可以由D/A生成模拟波形,由A/D实时采集,由DSP处理,对算法的设计和调试可带来很大的帮助。

系统通过实际测试,运行速度为40MIPS,程序和数据存储器、所有I/O口都能全速运行,工作稳定可靠。其工作流程如下:

(1)根据要求编写DSP程序并调试通过。

(2)复位DSP,并由主设备通过HPI接口向DSP下载程序。

(3)复位信号失效,DSP在主设备的控制下开始工作。

由于系统工作于较高的频率下(CPU为40MHz,外围设备一般为20MHz,最高为40MHz),因而在系统设计中,必须注意高频影响。

首先,系统要尽量简单,要选择大容量、表面封装的元器件,以使元件数量少、体积小,降低信号反射并有利于布线。

其次,在设计PCB板时,要采用四层板,中间两层作电源和地,并多加一些去耦电容。布线时不可用90度的拐弯,过孔要尽量少。数据和地址最好成组布线,以降低对其它信号的影响。一些关键的控制线,如存储器读写信号和FIFO读写信号,最好在其两边加地线保护。特别是FIFO的读写信号,由于其对干扰特别敏感,要特别注意。对一些较长的引线,可串接一个30Ω的小电阻或加终端匹配以减小反射。

4 C5000系列DSP的软件编程和调试

C5000系列DSP的编程工具,有C语言和汇编语言两种,而汇编语言又有两种指令集,一种叫记忆指令集(Mnemonic Instruction Set ,类似8086的汇编语言;一种叫代数指令集(Algebraic Instruction Set ,类似于C语言,使用起来比记忆指令集方便很多。

实际应用中,一般都是C和汇编混合编程,混合编程的方法,可查阅C5000系列DSP的手册得到。TI公司还提供了一个运行库(Runtime Lib ,用TI公司的JTAG调试器进行调试时,在DSP程序中调用运行库的函数,可以打开PC机上的文件获取数据,或将DSP的数据传入PC机并存入文件,或通过PC机键盘向DSP传递信息和发送命令,总之,可以为调试带来极大的方便。

在本系统中,由于既有A/D,又有D/A,构成了一个闭环,自发自收。可以由D/A生成模拟波形,由A/D实时采集,由DSP处理,对算法的设计和调试可带来很大的帮助。

|

|

|