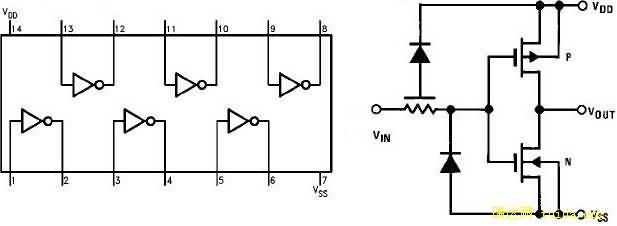

CC4069由六个COS/MOS反相器电路组成。此器件主要用作通用反相器、即用于不需要中功率TTL驱动和逻辑电平转换的电路中。838电子

CD4069引脚功能图

交流测试电路和波形切换时间

Absolute Maximum Ratings 绝对最大额定值:

DC Supply Voltage 直流供电电压 (VDD) -0.5V to +18 VDC Input Voltage输入电压 (VIN) -0.5V to VDD +0.5 VDC Storage Temperature Range储存温度范围 (TS) -65℃ to +150℃ Power Dissipation功耗 (PD) Dual-In-Line 普通双列封装 700 mW Small Outline 小外形封装 500 mW Lead Temperature 焊接温度(TL) Soldering, 10 seconds)(焊接10秒) 260℃

Recommended Operating Conditions 建议操作条件:

DC Supply Voltage 直流供电电压 (VDD) 3V to 15VDC Input Voltage输入电压 (VIN) 0V to VDD VDC Operating Temperature Range工作温度范围 (TA) -40℃ to +85℃

DC Electrical Characteristics 直流电气特性:

Symbol 符号

Parameter 参数 Conditions 条件 -40℃ +25℃ +85℃Units 单位

最小 最大 最小 典型最大最小最大IDD Quiescent Device Current静态电流 VDD=5V,VIN=VDD or VSS 1.0 1.0 7.5 μAVDD=10V,VIN=VDD or VSS 2.0 2.0 15 VDD=15V,VIN=VDD or VSS 4.0 4.0 30 VOL LOW Level Output Voltage 输出低电平电压 |IO| < 1μA VDD = 5V 0.05 0 0.05 0.05 V VDD = 10V 0.05 0 0.05 0.05 VDD = 15V 0.05 0 0.05 0.05 VOH HIGH Level Output Voltage 输出高电平电压 |IO| < 1 μA VDD = 5V 4.95 4.95 4.95 V VDD = 10V 9.95 9.95 9.95 VDD = 15V 14.95 14.95 14.95 VIL LOW Level Input Voltage 输入低电平电压 |IO| < 1 μA VDD = 5V, VO = 4.5V 1.0 1.0 1.0 VVDD = 10V, VO = 9V 2.0 2.0 2.0 VDD = 15V, VO = 13.5V 3.0 3.0 3.0 VIH HIGH Level Input Voltage 输入高电平电压 |IO| < 1 μA VDD = 5V, VO = 0.5V 4.0 4.0 4.0 VVDD = 10V, VO = 1V 8.0 8.0 8.0 VDD = 15V, VO = 1.5V 12.0 12.0 12.0 IOL LOW Level Output Current 输出低电平电流 (Note 4) VDD = 5V, VO = 0.4V 0.52 0.44 0.88 0.36 mA VDD = 10V, VO = 0.5V 1.3 1.1 2.25 0.9 VDD = 15V, VO = 1.5V 3.6 3.0 8.8 2.4 IOH HIGH Level Output Current 输出高电平电流 (Note 4) VDD = 5V, VO = 4.6V -0.52 -0.44 -0.88 -0.36 mA VDD = 10V, VO = 9.5V -1.3 -1.1 -2.25 -0.9 VDD = 15V, VO = 13.5V -3.6 -3.0 -8.8 -2.4 IIN Input Current 输入电流 VDD = 15V, VIN = 0V -0.30 -10-5 -0.30 -1.0 μAVDD = 15V, VIN = 15V 0.30 10-5 0.30 1.0

AC Electrical Characteristics 交流电气特性:

Symbol 符号

Parameter 参数 Conditions 条件 最小 典型 最大 Units 单位 tPHLor tPLH Propagation Delay Time from Input to Output 输入输出传播延迟时间VDD = 5V 50 90 ns VDD = 10V 30 60 VDD = 15V 2550tTHL or tTLH Transition Time过渡时间 VDD = 5V 80 150 nsVDD = 10V 50 100 VDD = 15V 4080CIN Average Input Capacitance 平均输入电容 Any Gate 6 15 pF CPD Power Dissipation Capacitance 功耗电容Any Gate(Note6) 12 pF

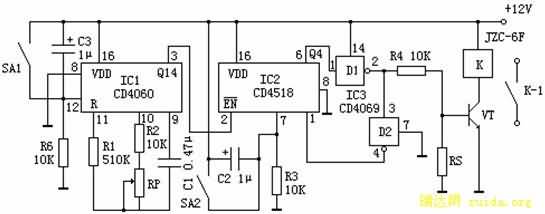

精确长延时电路

原理如上图所示。

通电后,时基振荡器震荡经过分频后向外输出时基信号。作为分频器的IC2开始计数分频。当计数到10时,Q4输出高电平,该高电平经D1反相变为低电平使VT截止,继电器断电释放,切断被控电路工作电源。与此同时,D1输出饿低电平经D2反相为高电平后加至IC2的CP端,使输出端输出的高电平保持。电路通电使IC1、IC2复位后,IC2的四个输出端,均为低电平。而Q4输出的低电平经D1反相变为高电平,通过R4使VT导通,继电器通电吸和。这种工作状态为开机接通、定时断开状态。

相关IC下载

LC864512―5C77/N801 LA7687A(N201) LA4285(N

AN5195K、AN5199、AN5265、AN5274、AN5521、AN5

AD9883APDF格式参考资料。

BA3880S、BA7001、BA7021等PDF格式参考资料

CTV222S等PDF格式参考资料

CXP84420-X133SP等PDF格式参考资料

KA9258D等PDF格式参考资料

LA4225、LA4285、LA4287、LA7680、LA7688A、LA7

LC863320A、LC864912A、LC864916A、等PDF格式参

M51393AP参考资料