在EMC设计中,电容是应用最广泛的元件之一,主要用于构成各种低通滤波器或用作去耦电容和旁路电容。大量实践表明:在EMC设计中,恰当选择与使用电容,不仅可解决许多EMI问题,而且能充分体现效果良好、价格低廉、使用方便的优点。若电容的选择或使用不当,则可能根本达不到预期的目的,甚至会加剧EMI程度。

本文根据EMC设计原理和不同结构电容的特点,结合相关研究的新进展,针对电容在EMC设计中的一些不恰当的认识与做法,讨论了电容在EMC设计中的应用技巧。对EMC设计具有指导作用。

滤波器结构的选择

EMC设计中的滤波器通常指由L,C构成的低通滤波器。不同结构的滤波器的主要区别之一,是其中的电容与电感的联接方式不同。滤波器的有效性不仅与其结构有关,而且还与连接的网络的阻抗有关。如单个电容的滤波器在高阻抗电路中效果很好,而在低阻抗电路中效果很差。

传统上,在滤波器两端的端接阻抗为50欧姆的条件下描述滤波器的特性(这一点往往未被注意),因为这样测试方便,并且是符合射频标准的。

但是,实践中源阻抗Zs和负载阻抗Zi很复杂,并且在要抑制的频率点上可能是未知的。如果滤波器的一端或两端与电抗性元件相联结,则可能会产生谐振,使某些频率点的插入损耗变为插入增益。

可见,正确选择滤波器的结构至关重要。究竟是选择电容、电感还是两者的组合,是由所谓的"最大不匹配原则"决定的。简言之,在任何滤波器中,电容两端存在高阻抗,电感两端存在低阻抗。图1是利用最大不匹配原则得到的滤波器的结构与ZS和ZL的配合关系,每种情形给出了2种结构及相应的衰减斜率(n表示滤波器中电容元件和电感元件的总数)。

但是,如何判定Z,和乙的值是高或低,一些资料上并未作具体说明[1,2],实践中也往往不清楚。

Zs和ZL的所谓的高值或低值的临界选取有一定的随机性,选取50n作为边界值是比较合适的。

顺便指出,在电子电路中,因信号一般较弱,而RC低通滤波器对信号有一定的衰减,故很少使用。

2 自谐振频率与截止频率

2.1 去耦电容的自谐振频率

实际的电容都有寄生电感Ls。Ls的大小基本上取决于引线的长度,对圆形、导线类型的引线,上'的典型值为10nH/cm[3]。典型的陶瓷电容的引线约有6 mm长,会引入约15nH的电感'"。引线电感也可由下式估算[4]:

其中:/和r分别为引线的长度和半径。

寄生电感会与电容产生串联谐振,即自谐振,在自谐振频率fo处,去耦电容呈现的阻抗最小,去耦效果最好。但对频率f高于f/o的噪声成份,去耦电容呈电感性,阻抗随频率的升高而变大,使去耦或旁路作用大大下降。实践中,应根据噪声的最高频率fmax来选择去耦电容的自谐振频率f0,最佳取值为fo=fmax。

但是,一些资料上只是从电容的寄生电感的角度给出了自谐振频率fo的资料。实际上,去耦电容的自谐振频率不仅与电容的寄生电感有关,而且还与过孔的寄生电感[5]、联结去耦电容与芯片电源正负极引脚的印制导线的寄生电感[6.7]等都有关系。如果不注意这一点,查得的资料或自己的估算往往与实际情况相去甚远。

实践中,一般是先确定去耦电容的结构(电容的寄生电感与其结构关系密切),再用试验的方法确定容量。

2.2 电源滤波器的钓自谐振频率

在交流电源进线与电源变压器之间设置电源滤波器是抗EMI的常用措施之一。常用的电源滤波器如图2所示。人们一般对去耦电容的自谐振频率问题比较注意,实际上电源滤波器也有自谐振频率问题,处理不当,同样达不到预期的目的。

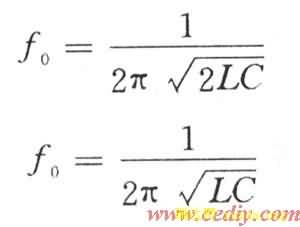

对图2所示的滤波器,分析可知,当电感的电阻rL很小时,自谐振频率分别为:

设计电源滤波器时,必须使滤波器的自谐振频率远小于噪声频率。处理不当.不仅不能衰减噪声,反而会放大噪声。

例如[8]图2(a)所示的滤波器,如果取L=1 mH,rL=1欧姆,C=0.47 uF(这也是许多资料上推荐的参数),可算出f0=5.2 kHz。而EMC测试中的快速脉冲群频率为5.0kHz(2kV)或2.5kHz(4kV),5.0kHz刚好谐振,2.5kHz也不会被衰减,如图3所示。这说明滤波器中元件参数选取不当,可能根本起不到提高EMC性能的作用。

3.电容结构的选择

从理论上讲,电容的容量越大,容抗就越小,滤波效果就越好。一些人也有这种习惯认识。但是,容量大的电容一般寄生电感也大,自谐振频率低(如典型的陶瓷电容,0.1 uF的fo=5MHz,0.01ulF的fo=15MHz,0.001uF的f0=50MHz),对高频噪声的去耦效果差,甚至根本起不到去耦作用。分立元件的滤波器在频率超过10MHz时,将开始失去性能。元件的物理尺寸越大,转折点频率越低。这些问题可以通过选择特殊结构的电容来解决。

贴片电容的寄生电感几乎为零,总的电感也可以减小到元件本身的电感、通常只是传统电容寄生电感的1/3~1/5,自谐振频率可达同样容量的带引线电容的2倍(也有资料说可达10倍),是射频应用的理想选择。

传统上,射频应用一般选择瓷片电容。但在实践中,超小型聚脂或聚苯乙烯薄膜电容也是适用的,因为他们的尺寸与瓷片电容相当。

三端电容能将小瓷片电容频率范围从50MHz以下拓展到200MHz以上,这对抑制VHF频段的噪声是很有用的。要在VHF或更高的频段获得更好的滤波效果,特别是保护屏蔽体不被穿透,必须使用馈通电容。

4 电容容量的选择

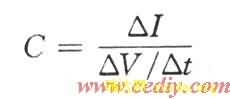

在数字系统中,去耦电容的容量通常按下式估算:

其中:/xl为瞬变电流;AV为逻辑器件允许的电源电压变

此外,当电源引线比较长时,瞬变电流会引起较大的压降,此时就要加容纳电容以维持器件要求的电压值。

5 去耦电容的安装方式与PCB设计

安装去耦电容时,一般都知道使电容的引线尽可能短。但是,实践中往往受到安装条件的限制,电容的引线不可能取得很短。况且,电容引线的寄生电感只是影响目谐振频率的因素之一,自谐振频率还与过孔的寄生电感、相关印制导线的寄生电感等因素有关。一味地追求引线短,不仅困难,而且根本达不到目的。

这说明要保证去耦效果,在PCB设计时,就要考虑相关问题。设计印制导线时,应使去耦电容距离芯片电源正负极引脚尽可能近(当然电容引线要尽可能短)。设计过孔时应尽量减小过孔的寄生电感。

6 结 语

人们不断纠正或放弃电容在EMC设计中的一些传统认识与做法。电容在EMC设计中的作用大小与多种因素有关,巳其中的很多因素一直在不断的研究与变化中。所以,要充分发挥电容在EMC设计中的作用,及时了解相关研究的新进展,及时采用新技术,是非常重要的。

|

|

|